안녕하세요. RTLog입니다.

이번에는 지난 내용에 이어서 Timing Constraint에 대해서 작성해보려고 합니다.

Timing Constraint

지난 포스트에서는 Setup/Hold Time, Contamination/Propagation Delay에 대해 설명했었는데요.

이런 개념들이 Timing Constraint로 어떻게 이어지는지 설명해보려고 합니다.

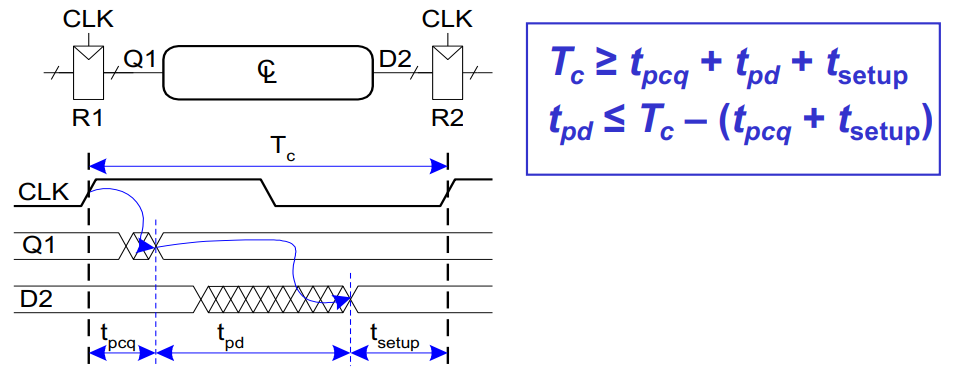

Setup Time Constraint

지난 포스트에서 T_setup, T_pcq는 공정의 특성으로 결정된다고 말씀드렸습니다. 따라서, T_setup에 대한 Violation이 발생하는 경우 회로의 정확한 동작을 보장할 수 없고, 이를 방지하기 위해서는 파란색 박스의 부등식을 만족해야 합니다.

Clock Period가 Clock to Q Propation Delay, Logic Propagation Delay, Setup Time의 합보다 커야한다는 것인데, Timing 다이어그램으로 직관적인 이해가 가능하실 것 같습니다. 그렇다면 Setup Time Violation이 발생한 경우 어떻게 대처해야 할까요? "T_setup, T_pcq는 공정의 특성으로 결정"에 힌트가 있습니다.

회로 설계자의 변경할 수 있는 권한은 T_pd만 남았으니까요. Logic Propagation Delay를 줄이기 위해 Pipelining Stage를 나누어 Multi-Cycle로 변경하거나, 연산기를 많이 써서 딜레이를 낮추는 등의 방법으로 T_pd를 낮출 수 있습니다. (단순히, Clock Frequency를 낮추는 것도 방법일 수 있습니다.)

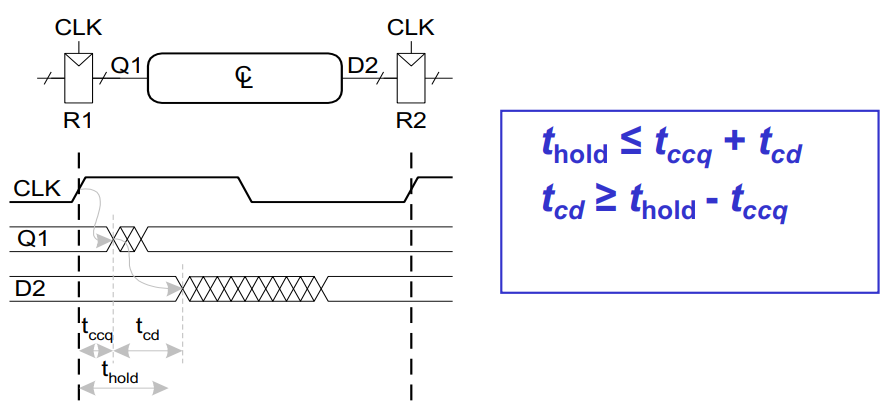

Hold Time Constraint

마찬가지로, T_hold, T_ccq는 공정의 특성으로 결정된다고 말씀드렸습니다. 따라서, T_hold에 대한 Violation이 발생하는 경우 회로의 정확한 동작을 보장할 수 없고, 이를 방지하기 위해서는 파란색 박스의 부등식을 만족해야 합니다.

Hold Time 동안은 데이터의 Stable한 상태를 보장해야 하기 때문에, 데이터가 가장 빠르게 변하는 시점인 Clock to Q contamination delay와 Logic contamination delay의 합이 Hold Time보다 길어야 한다는 것입니다.

Hold Time Violation이 발생하면 어떻게 해야 할까요? 가장 간단한 방법은 지연을 만들어주는 Buffer를 의도적으로 삽입하여 Logic Contamination Delay를 늘려주는 방법이 있습니다.

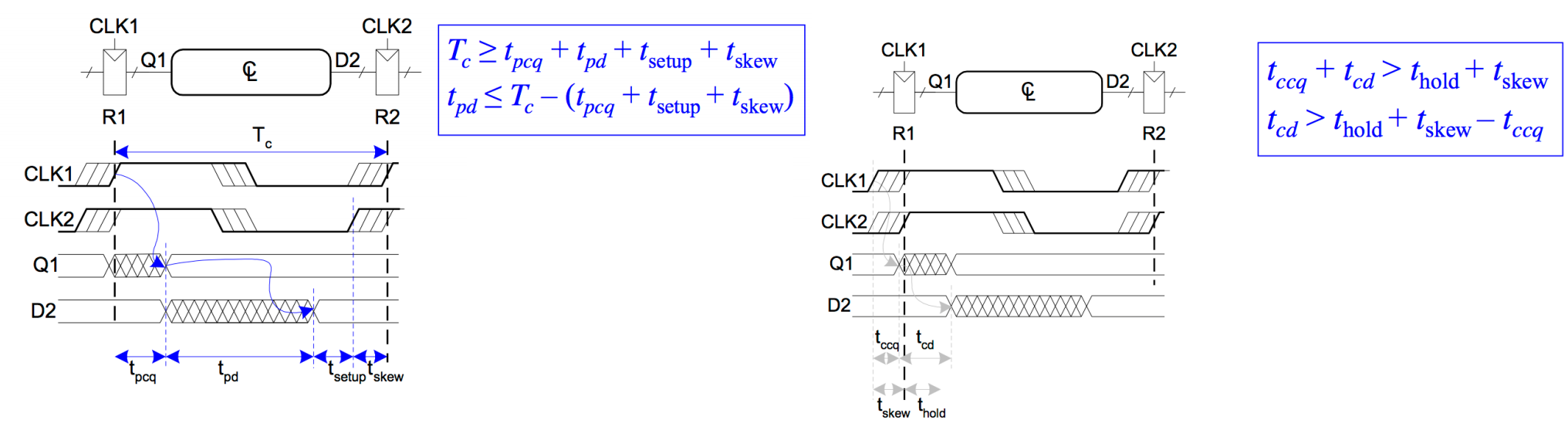

Setup/Hold Time Constraint with Skew

Skew Time

마지막으로, Skew Time에 대해 소개하려고 합니다.

HDL로 작성된 코드를 Synthesis하면, Netlist가 추출됩니다. (Netlist는 게이트 레벨의 회로라고 생각하시면 됩니다.)

이후, Netlist(Gate, F/F, ...)를 배치하고 연결하는 과정인 Place & Routing 과정을 통해 Chip을 만들게 되죠.

Place & Routing 과정에서 F/F이 칩 내에서 어떤 위치에 배치되고 어떻게 연결되는지에 따라 각각의 F/F에 전달되는 Clock Timing이 흔들릴 수 있습니다. 간단하게, 모든 F/F에 도착하는 Clock 시간이 칩 내부 거리에 따라 달라진다는 것이죠. 이에 따라 발생하는 시간의 오차를 Skew Time이라고 합니다.

Skew Time을 최소화하기 위한 방법은 Clock Tree Synthesis(CTS)가 있습니다. 같은 타이밍에 전달되어야 하는 Clock을 Clock Tree의 동일 계층에 배치하는 방법입니다.

Timing Constraint

Skew Time은 Timing Constraint에 어떤 영향을 미칠까요?

* R1에 Clock이 먼저 도착할 수도 있고 R2에 Clock이 먼저 도착할 수도 있음

Setup Time Constraint에서는 Clock의 전달시간을 고려하여 Clock Period를 충분히 길게 설정해야 하고, Hold Time에서는 Skew Time에 의해 값의 변화가 빨라질 수 있는 상황에 대비해서 Logic Contamination Delay를 더 길게 사용해야 합니다.

마지막으로 중요한 점은 회로의 최대 동작 주파수가 Setup Time 부등식에서 등호인 경우에 해당한다는 것입니다. 동작 주파수를 높이기 위해서는 공정에 의존하는 요소도 중요하지만, Logic Propagation Delay가 중요한 것을 알 수 있습니다.

오늘은 여기까지 해볼게요.

감사합니다.

'Digital Design > 설계 방법론' 카테고리의 다른 글

| Timing Analysis (1) - Setup/Hold/Contamination/Propagation (0) | 2024.02.28 |

|---|